集成電路可測性設計中網表的解析與實現 構建可靠芯片的基石

在當今高度數字化的時代,集成電路(IC)已滲透到從消費電子到航空航天等各個領域。隨著芯片工藝節點不斷縮小,設計復雜度呈指數級增長,確保芯片在制造后能夠被有效、高效地測試,已成為設計流程中不可或缺的關鍵環節。可測性設計(Design for Testability, DFT)正是為了解決這一挑戰而誕生的一系列設計方法和技術。而在DFT的整個實現流程中,對網表的解析、處理與最終實現,構成了連接邏輯設計與物理實現、確保測試質量的核心橋梁。

一、 網表:芯片設計的“電路藍圖”

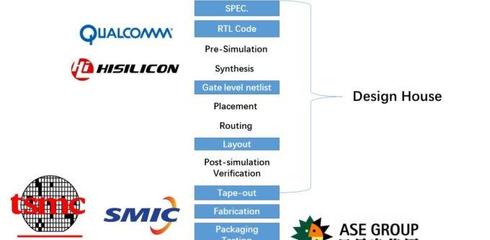

網表(Netlist)是集成電路設計從高層次抽象描述(如RTL代碼)向物理版圖轉換過程中的一種中間表示形式。它本質上是一個由邏輯門(如與門、或門、非門、觸發器等標準單元)以及這些單元之間的互連關系(連線或網絡)構成的圖結構。網表精確描述了芯片的邏輯功能,但不包含具體的物理布局和時序信息。在DFT語境下,網表是插入和實現各類可測試性結構(如掃描鏈、內建自測試BIST、邊界掃描等)的直接操作對象。

二、 網表解析:理解設計的結構與約束

網表解析是DFT流程的第一步,其目標是將網表文件(通常是Verilog、VHDL或EDIF格式)讀入DFT工具的內存中,構建起一個可供查詢、分析和修改的內部數據模型。這一過程看似簡單,實則至關重要,它要求工具能夠:

- 準確識別層次結構:大型設計通常采用層次化設計方法。解析器必須正確處理模塊實例化、端口映射和層次邊界,構建出清晰的層次樹,以便后續操作能準確定位到目標模塊或實例。

- 理解設計意圖:解析過程中需要識別和保留設計中已有的特殊結構,例如時鐘網絡、復位網絡、三態總線、模擬模塊等。這些結構對DFT策略有直接影響,必須被妥善處理。

- 加載設計約束:與網表一同解析的還有時序約束文件(如SDC文件),其中定義了時鐘、時序路徑、虛假路徑等關鍵信息。正確的DFT實現必須嚴格遵守這些約束,以免引入時序違規。

三、 網表實現:DFT結構的插入與集成

在成功解析并分析了原始網表之后,便進入DFT結構的具體實現階段。這是將測試理念轉化為實際電路的關鍵步驟,主要包括:

- 掃描鏈插入與連接:這是最核心的DFT技術之一。工具需要:

- 掃描單元替換:將設計中的普通觸發器(D Flip-Flop)替換為具有掃描功能的觸發器(Scan Flip-Flop),該觸發器擁有正常的數據輸入端(D)、掃描數據輸入端(SI)、掃描使能端(SE)和時鐘端。

- 掃描鏈 stitching:按照預設的掃描鏈配置(鏈數、長度、順序),將所有掃描觸發器的掃描輸出(SO)連接到下一個掃描觸發器的掃描輸入(SI),形成一條或多條完整的掃描路徑。這個過程需要優化繞線長度、平衡鏈長,并考慮時鐘域和物理布局的約束。

- 測試控制信號集成:將掃描使能(SE)、測試時鐘(ATPG Clock)、測試模式選擇等全局測試控制信號集成到設計中,并確保它們能被測試儀準確控制。

- 測試壓縮邏輯插入:為了應對海量測試數據帶來的測試時間和存儲成本壓力,現代DFT廣泛采用測試壓縮技術(如嵌入式確定性測試EDT)。這需要在掃描鏈的輸入輸出端插入壓縮/解壓縮邏輯(如線性反饋移位寄存器LFSR、解壓器、壓縮器),并在網表中實現這些模塊與掃描鏈的對接。

- 內存BIST(MBIST)與邏輯BIST(LBIST)集成:對于芯片中的嵌入式存儲器(RAM/ROM)和隨機邏輯,需要插入專門的內建自測試控制器。這涉及到在網表中實例化BIST控制器模塊,并將其與待測的存儲器或邏輯模塊正確連接,同時處理好測試模式下的時鐘、使能和數據通路。

- 邊界掃描(JTAG)的實現:為了支持板級和系統級測試,需要在芯片頂層實現符合IEEE 1149.1標準的JTAG(邊界掃描)接口和控制器。這包括在芯片I/O端口插入邊界掃描單元(BSC),并將其連接到TAP(測試訪問端口)控制器,形成完整的邊界掃描鏈。

四、 實現后的驗證與交付

DFT結構插入完成后,生成的是一個經過修改的新網表(通常稱為DFT網表或測試模式網表)。此時必須進行嚴格的驗證,包括:

- 功能等價性檢查(Formal Equivalence Checking):確保DFT網表與原始網表在功能模式(非測試模式)下完全等價。

- 設計規則檢查(DFT DRC):檢查掃描鏈是否完整、有無懸空端口、時鐘混合、異步復位處理等是否符合DFT規則。

- 測試模式生成與仿真(ATPG & Simulation):利用新的DFT網表生成測試向量(Test Patterns),并進行仿真,驗證這些向量能否有效檢測目標故障(如stuck-at, transition faults),并確保測試過程中的功耗等指標在安全范圍內。

驗證無誤后,這個集成了完整DFT結構的網表將與物理設計工具(布局布線工具)進行交付,進入后端實現階段。后端工具將基于此網表進行布局、布線、時鐘樹綜合和時序簽核,最終生成可用于制造的光刻掩模版(GDSII文件)。

五、 挑戰與未來趨勢

網表的解析與實現面臨諸多挑戰:超大規模設計帶來的處理性能與容量問題;低功耗設計(多電壓域、電源門控)與DFT的協同;先進工藝下新型缺陷模型的測試需求;以及日益重要的系統級測試和硅后調試支持等。

隨著人工智能和機器學習技術的應用,DFT工具在網表解析優化、掃描鏈自動平衡、測試點智能插入等方面將變得更加自動化與智能化。基于云平臺的DFT解決方案也將助力處理更大規模的設計數據。

###

總而言之,網表的解析與實現是集成電路可測性設計從理論方案落地為硬件電路的核心工程環節。它要求工程師不僅精通DFT原理,還需深刻理解設計本身、后端物理約束以及芯片測試的全流程。精準、高效地完成這一步驟,是確保芯片具備高質量可測試性,從而提升產品良率、降低總體成本、保障最終產品可靠性的堅實基石。

如若轉載,請注明出處:http://m.szldl.cn/product/84.html

更新時間:2026-02-28 18:19:20